Home

# Zynq SDR Course

**Engineering-grade SDR course: from mathematical model to measured RF signal**

This site is the main course workspace. It connects theory, MATLAB/Simulink modeling, fixed-point DSP, FPGA implementation, AD9363 RF hardware, RTL-SDR reception, IQ recording and reproducible analysis.

MATLAB / Simulink

Fixed-point DSP

FPGA / HDL

Zynq-7020

AD9363

RTL-SDR

Core engineering route¶

flowchart TB

MODEL["1. Model and reference signal<br/>MATLAB / Simulink, ideal floating-point behavior"]

FIXED["2. Fixed-point conversion<br/>word length, scaling, overflow and quantization noise"]

FPGA["3. FPGA implementation<br/>streaming DSP blocks, latency, AXI interfaces"]

RF["4. RF frontend<br/>AD9363 frequency plan, gain, filters and bandwidth"]

CHANNEL["5. Physical channel<br/>coax with attenuation or controlled over-the-air path"]

RX["6. Independent receiver<br/>RTL-SDR + HDSDR for external observation"]

IQ["7. IQ recording<br/>WAV / RAW / CI16 with documented metadata"]

METRICS["8. Engineering metrics<br/>FFT, SNR, EVM, BER and final conclusion"]

MODEL --> FIXED --> FPGA --> RF --> CHANNEL --> RX --> IQ --> METRICS

METRICS -. redesign algorithm .-> MODEL

METRICS -. retune RF parameters .-> RFMain idea

The course is not simulation-only. Every important model decision must eventually be connected to a hardware signal and verified through measured data.

What you will build¶

1. Signal model

Reference waveforms, sample-rate planning, modulation, filtering and expected spectra.

2. Fixed-point DSP

Scaling, quantization, coefficient precision, overflow control and hardware-oriented validation.

3. FPGA signal path

DDS/NCO, mixer, FIR, interpolation, AXI-Stream and real-time processing on Zynq.

4. RF measurement loop

AD9363 transmit path, external reception through RTL-SDR, HDSDR observation and IQ recording.

Course quality pack¶

These pages turn the repository into a more complete engineering course workspace:

| Page | Purpose |

|---|---|

| Course quality roadmap | Defines the target level, checklist and backlog for course completion |

| Lab report template | Gives a repeatable structure for each DSP/RF/FPGA lab report |

| IQ recording metadata guide | Standardizes real-signal captures so measurements can be reproduced |

Hardware baseline¶

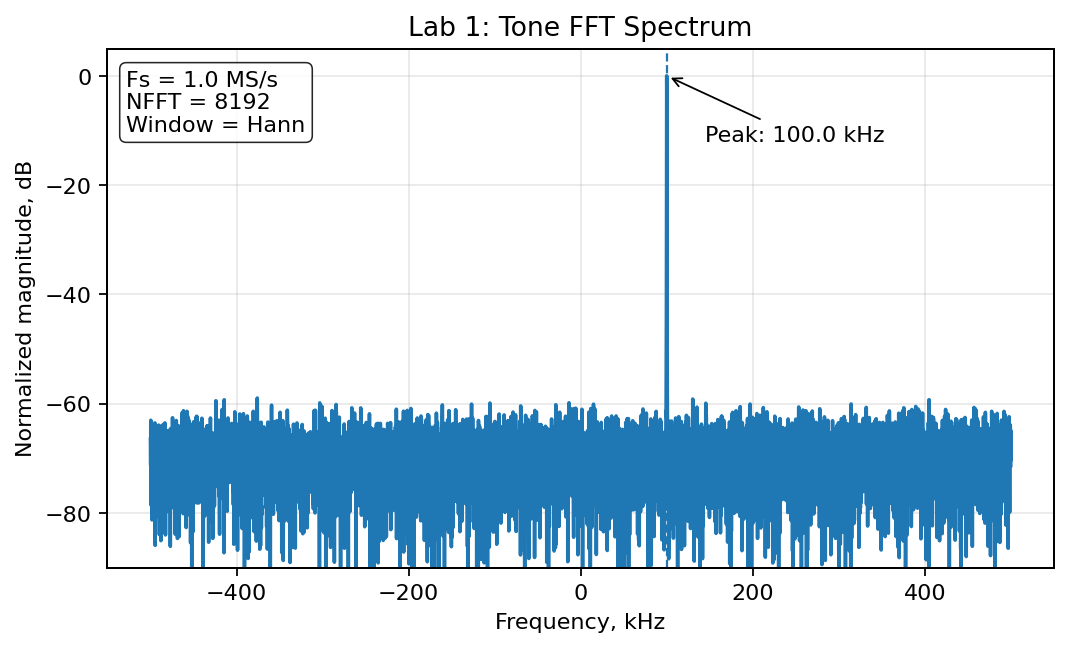

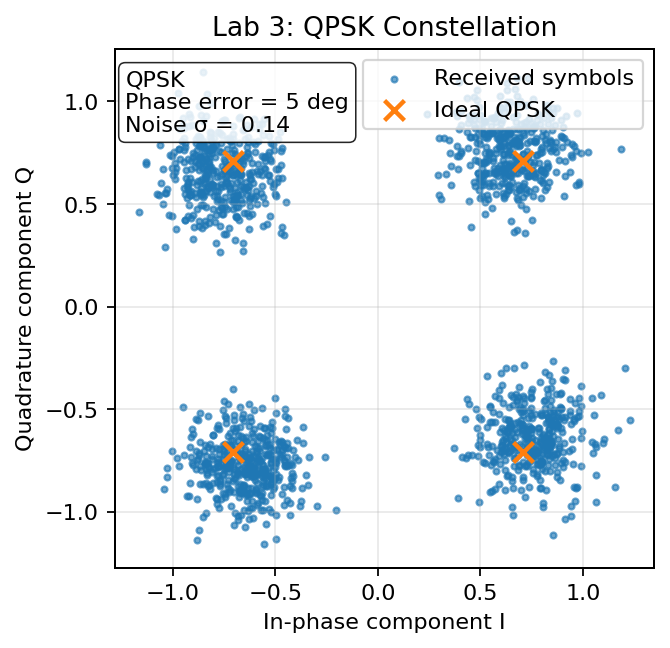

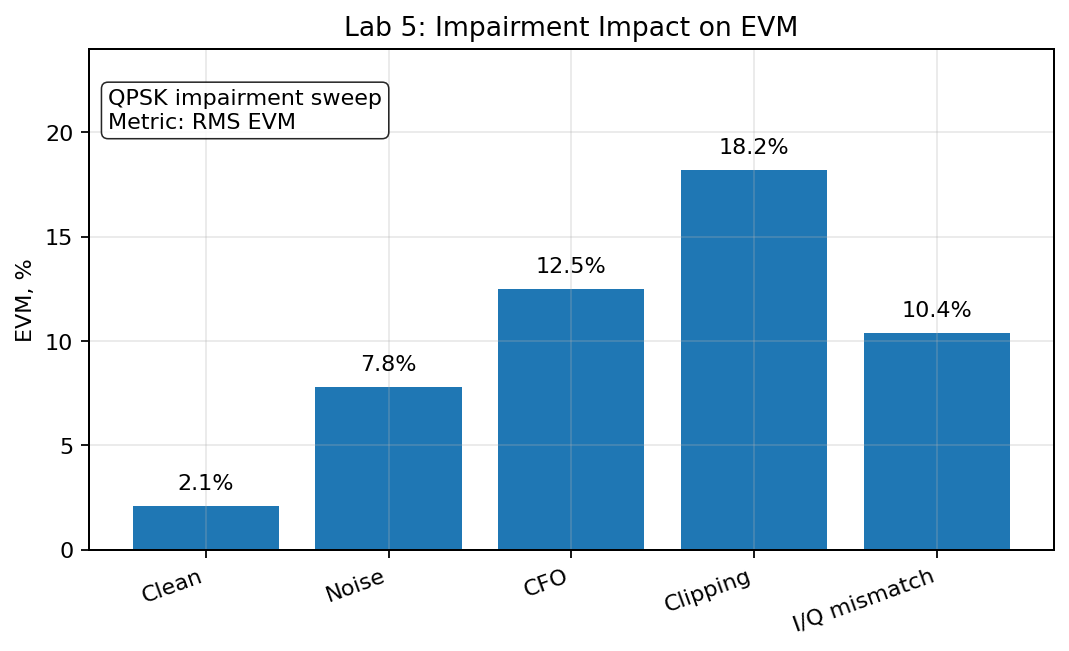

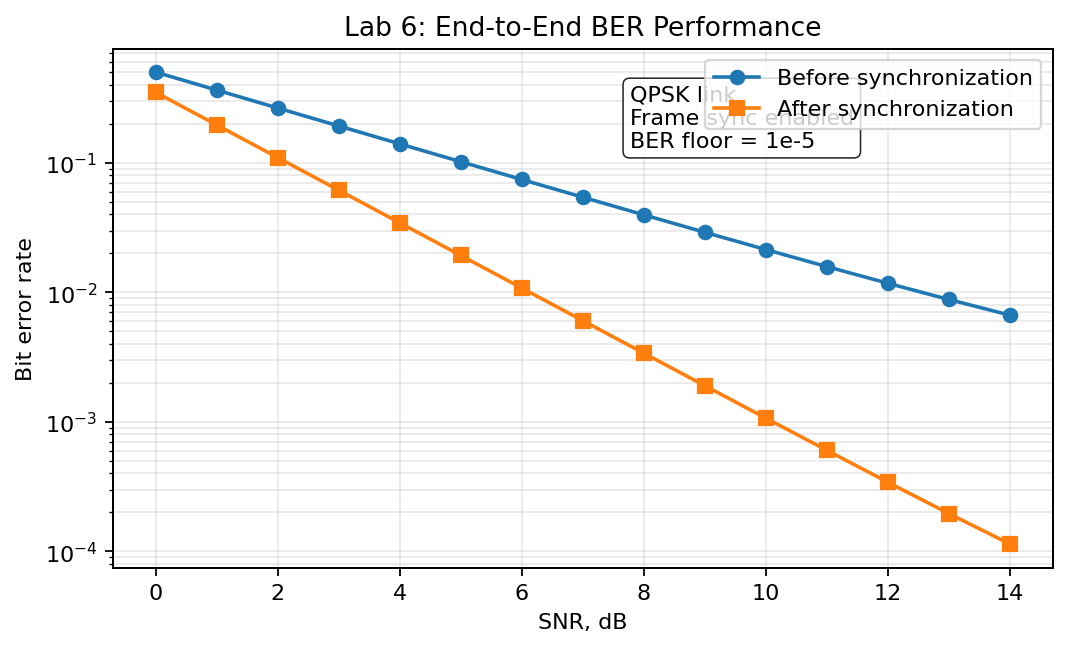

IEEE-style generated figures¶

Learning tracks¶

| Track | Start here | Engineering output |

|---|---|---|

| System view | Model → FPGA → RF → Measurement | End-to-end understanding of the SDR stand |

| Demo figures | IEEE-style figures | Reproducible plots and validation examples |

| Russian course | Русский обзор | RU learning path and block navigation |

| English course | English overview | EN learning path and block navigation |

Reproducibility¶

bash tools/reproduce_all.sh

mkdocs serve

The project is designed so that figures, documentation and the learning path can evolve together through GitHub Actions and MkDocs.